# SILICON LABS SIM3L1XX REFERENCE MANUAL

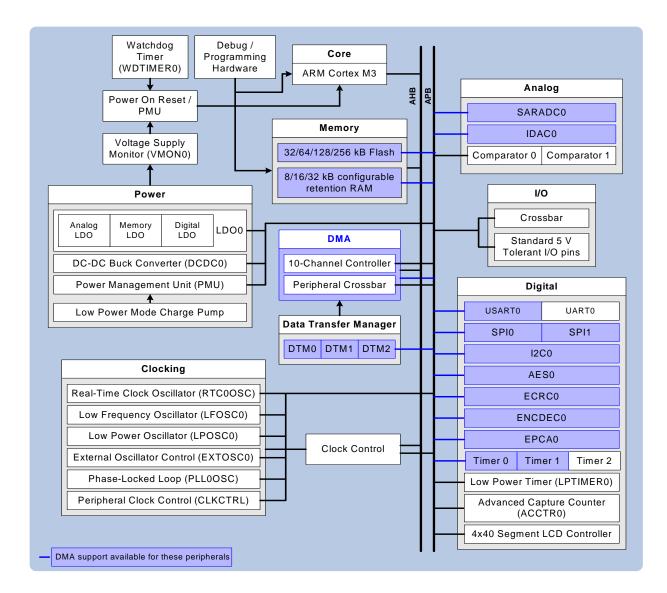

This reference manual accompanies several documents to provide the complete description of SiM3L1xx devices, part of the Silicon Laboratories 32-bit ARM Cortex-M3 family of microcontrollers.

This document provides a detailed description for all peripherals available on all SiM3L1xx devices. The peripheral mix varies across different members of the device family. Refer to the device data sheet for details on the specific peripherals available for each member of the device family. In the event that the device data sheet and this document contain conflicting information, the device data sheet should be considered the authoritative source.

### **Table of Contents**

| 1. | Related Documents and Conventions                                             | .11 |

|----|-------------------------------------------------------------------------------|-----|

|    | 1.1. Related Documents                                                        | .11 |

|    | 1.2. Conventions                                                              |     |

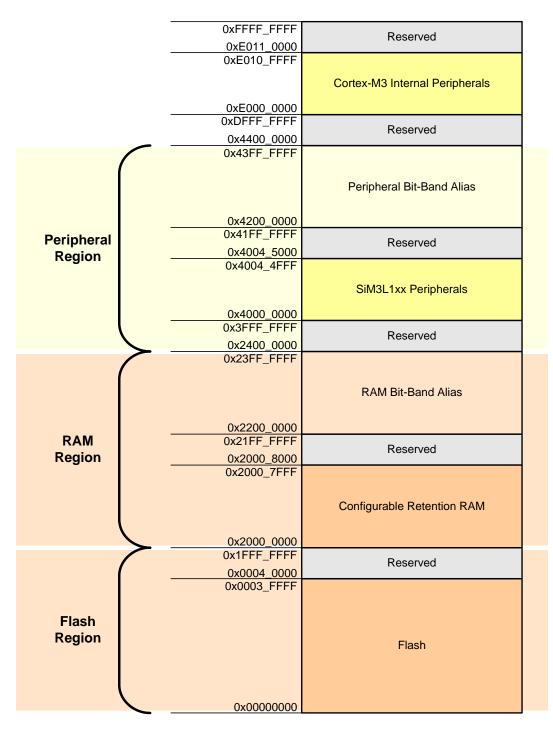

| 2. | Memory Organization                                                           |     |

|    | 2.1. Flash Region                                                             | .13 |

|    | 2.2. RAM Region                                                               | .14 |

|    | 2.3. Peripheral Region                                                        |     |

|    | 2.4. Cortex-M3 Internal Peripherals                                           |     |

|    | SiM3L1xx Register Memory Map                                                  |     |

| 4. | Interrupts                                                                    |     |

|    | 4.1. System Exceptions.                                                       |     |

|    | 4.2. Interrupt Vector Table                                                   |     |

| _  | 4.3. Priorities                                                               |     |

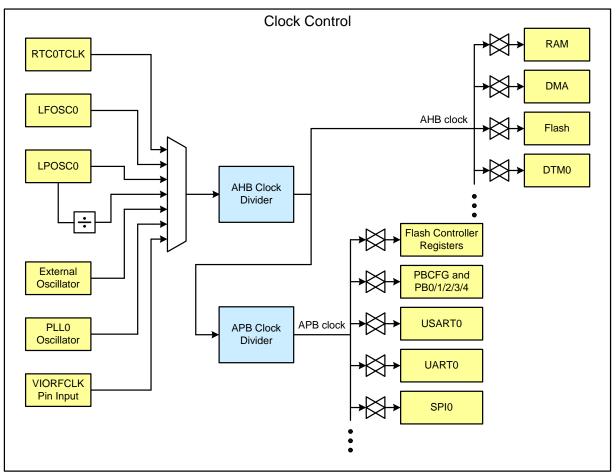

| 5. | Clock Control (CLKCTRL0)                                                      |     |

|    | 5.1. Clock Control Features                                                   |     |

|    | 5.2. CLKCTRL0 Registers                                                       | .39 |

| •  | 5.3. CLKCTRL0 Register Memory Map                                             |     |

| 6. | System Configuration (SCONFIG0)                                               |     |

|    | 6.1. System Configuration Features                                            |     |

|    | 6.2. SCONFIG0 Registers                                                       | .51 |

| 7  | 6.3. SCONFIG0 Register Memory Map                                             |     |

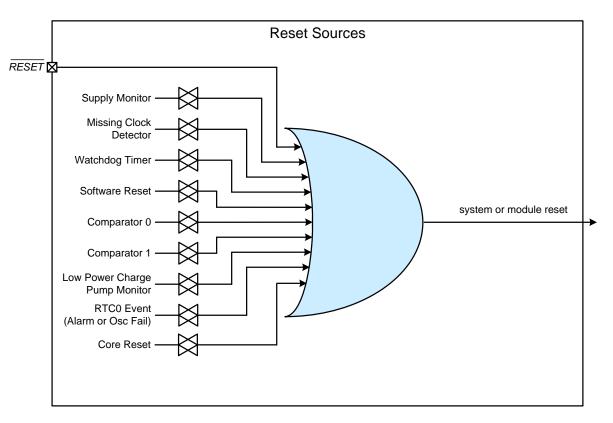

| 1. | Reset Sources (RSTSRC0)                                                       |     |

|    | 7.1. Reset Sources Features                                                   |     |

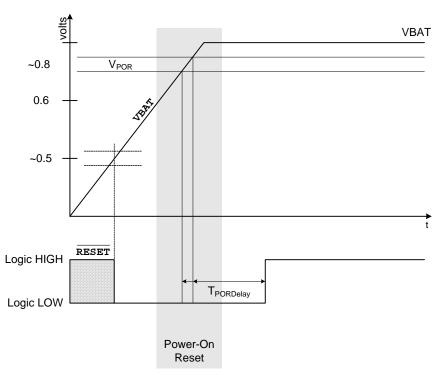

|    | 7.3. Power-On Reset                                                           |     |

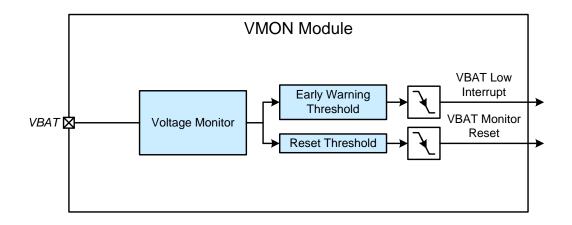

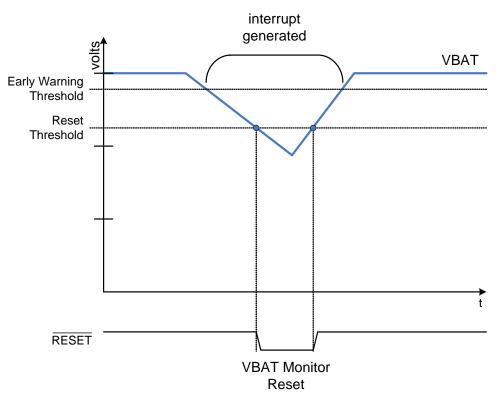

|    | 7.4. VBAT Monitor Power-Fail Reset                                            |     |

|    | 7.5. External Pin Reset                                                       |     |

|    | 7.6. Missing Clock Detector Reset                                             |     |

|    | 7.7. Comparator Reset                                                         |     |

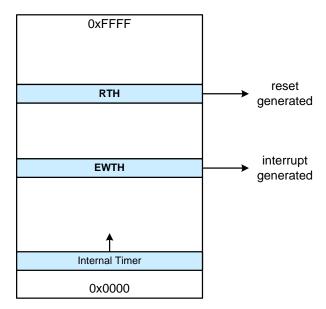

|    | 7.8. Watchdog Timer Reset                                                     |     |

|    | 7.9. RTC Reset                                                                |     |

|    | 7.10.Software Reset                                                           |     |

|    | 7.11.Core Reset                                                               |     |

|    | 7.12.PMU Wake Reset Flag                                                      |     |

|    | 7.13.RSTSRC0 Registers                                                        |     |

|    | 7.14.RSTSRC0 Register Memory Map                                              | .62 |

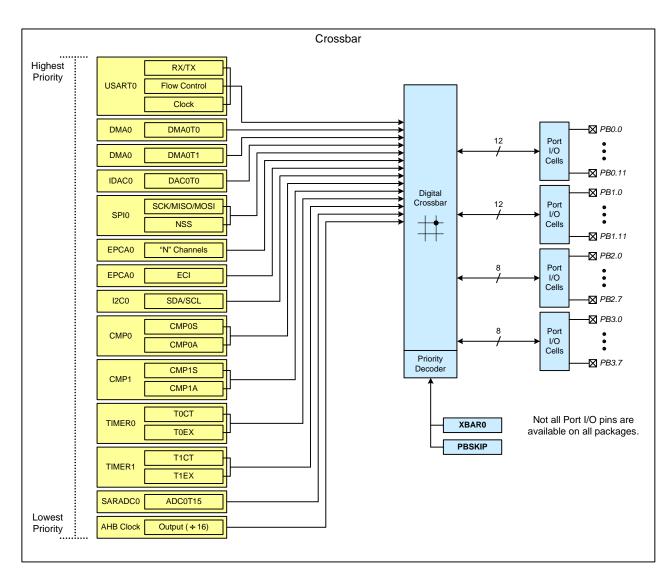

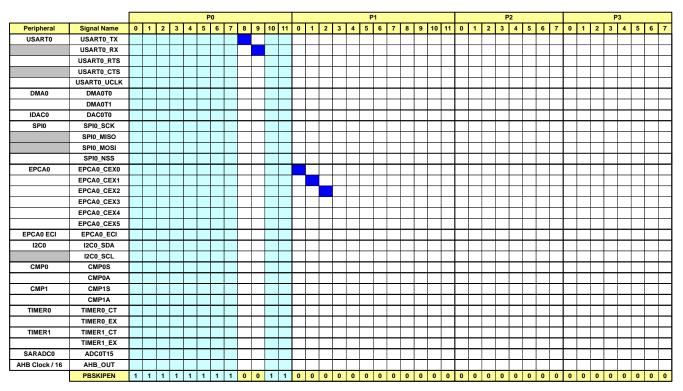

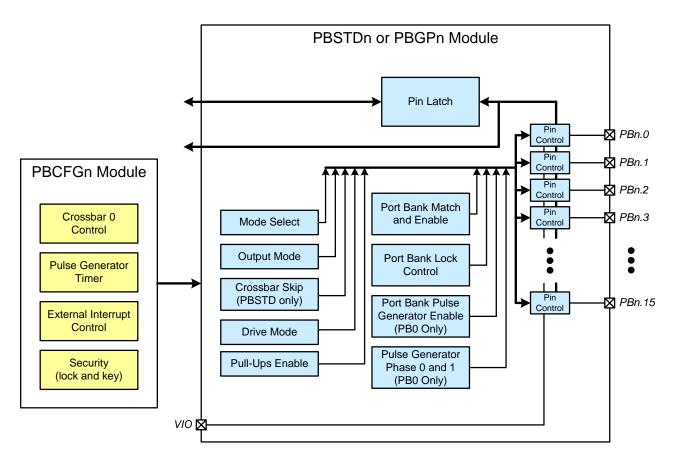

| 8. | Port I/O Configuration                                                        |     |

|    | 8.1. Port Bank Description                                                    |     |

|    | 8.2. Crossbar                                                                 |     |

|    | 8.3. Port Bank Standard (PBSTD) and Port Bank General Purpose (PBGP) Features |     |

|    | 8.4. Standard Modes of Operation                                              |     |

|    | 8.5. Assigning Standard Port Bank Pins to Analog and Digital Functions        |     |

|    | 8.6. Port Match                                                               | .70 |

|    | 8.7. Pulse Generator                                                          | .70 |

|    | 8.8. Port Bank Security                                             |     | 71 |

|----|---------------------------------------------------------------------|-----|----|

|    | 8.9. Debugging Interfaces                                           |     |    |

|    | 8.10.External Interrupts                                            |     |    |

|    | 8.11.PBCFG0 Registers                                               |     |    |

|    | 8.12.PBCFG0 Register Memory Map                                     |     |    |

|    | 8.13.PBSTD0, PBSTD1, PBSTD2 and PBSTD3 Registers                    |     | 84 |

|    | 8.14.PBSTDn Register Memory Map                                     |     |    |

|    | 8.15.PBGP4 Registers                                                |     |    |

|    | 8.16.PBGP4 Register Memory Map                                      |     |    |

| 9. | Power                                                               |     |    |

|    | 9.1. Power Modes                                                    |     |    |

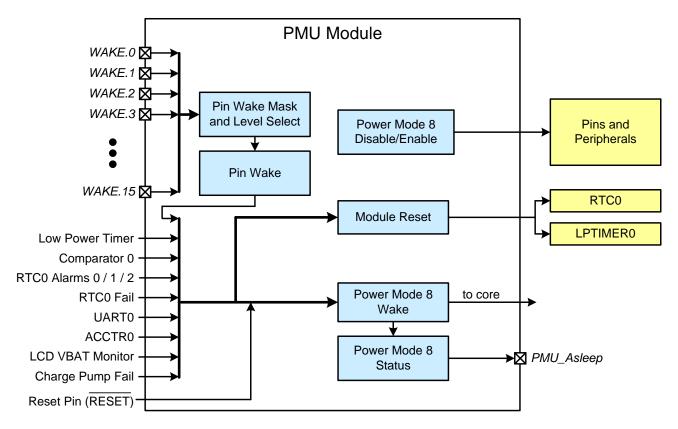

| 10 | .Power Management Unit (PMU0)                                       |     |    |

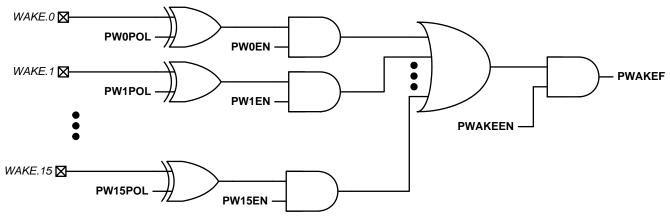

|    | 10.1.Waking from Power Mode 8.                                      |     |    |

|    | 10.2.Retention RAM Control                                          |     |    |

|    | 10.3.PMU0 Registers                                                 | . 1 | 15 |

|    | 10.4.PMU0 Register Memory Map                                       |     |    |

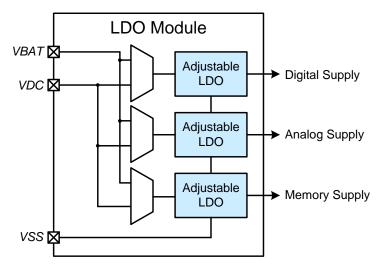

| 11 | Internal Voltage Regulator (LDO0)                                   | 1   | 30 |

|    | 11.1.Internal Voltage Regulator Features                            |     |    |

|    | 11.2.Functional Description                                         |     |    |

|    | 11.3.LDO0 Registers                                                 | . 1 | 32 |

|    | 11.4.LDO0 Register Memory Map                                       | . 1 | 34 |

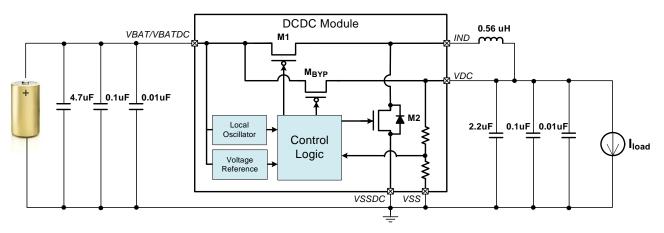

| 12 | DC-DC Regulator (DCDC0)                                             | 1   | 35 |

|    | 12.1.DCDC Features                                                  | . 1 | 35 |

|    | 12.2.Inductor Selection and Startup Behavior                        | . 1 | 36 |

|    | 12.3.Synchronous/Asynchronous Modes                                 | . 1 | 37 |

|    | 12.4.Power Switch Size                                              | . 1 | 38 |

|    | 12.5.Configuration Guidelines                                       |     |    |

|    | 12.6.Optimizing Board Layout                                        | . 1 | 38 |

|    | 12.7.Clocking Options                                               | 1   | 38 |

|    | 12.8.Bypass Mode                                                    | . 1 | 39 |

|    | 12.9.Interrupts                                                     | . 1 | 39 |

|    | 12.10.DCDC0 Registers                                               | . 1 | 40 |

|    | 12.11.DCDC0 Register Memory Map                                     |     |    |

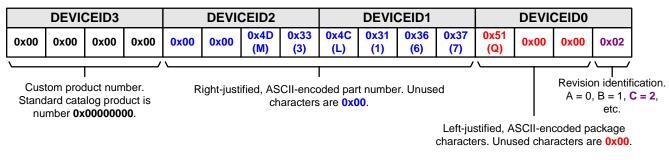

| 13 | Device Identification (DEVICEID0) and Universally Unique Identifier |     |    |

|    | 13.1.Device ID Features                                             |     |    |

|    | 13.2.Device Identification Encoding                                 |     |    |

|    | 13.3.Universally Unique Identifier (UUID)                           |     |    |

|    | 13.4.DEVICEID0 Registers                                            | . 1 | 47 |

|    | 13.5.DEVICEID0 Register Memory Map                                  | . 1 | 51 |

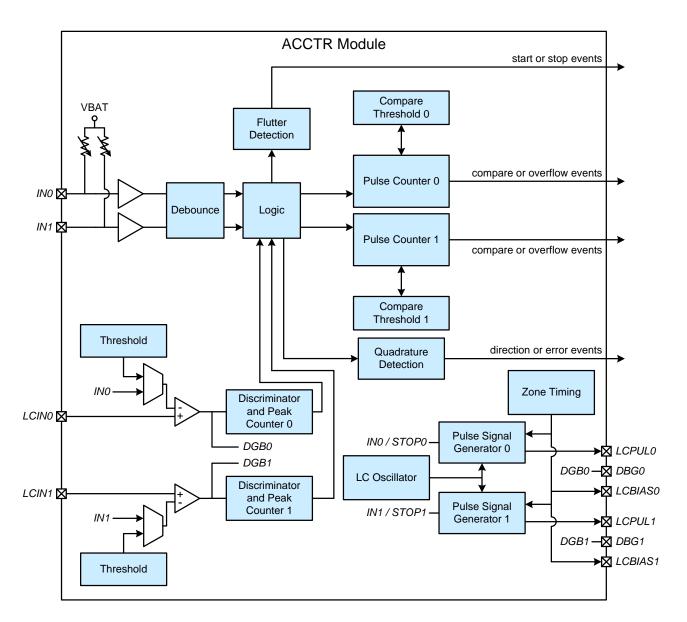

| 14 | Advanced Capture Counter (ACCTR0)                                   |     |    |

|    | 14.1.ACCTR Features                                                 |     |    |

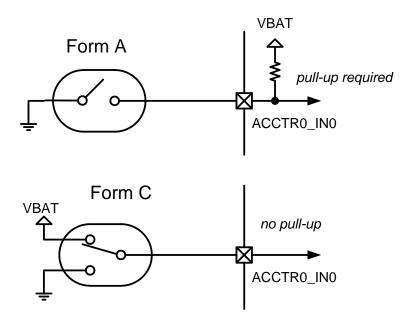

|    | 14.2.External Pin Connections                                       |     |    |

|    | 14.3.Overview                                                       |     |    |

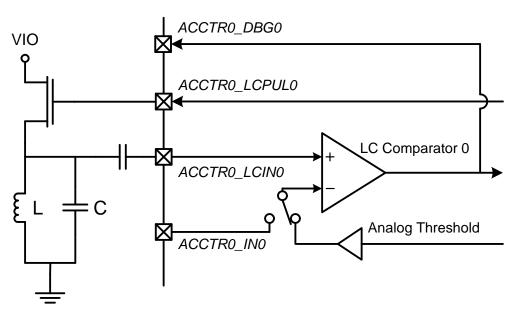

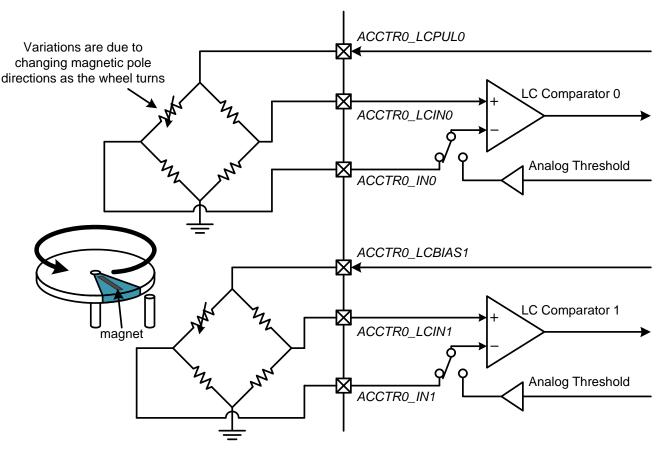

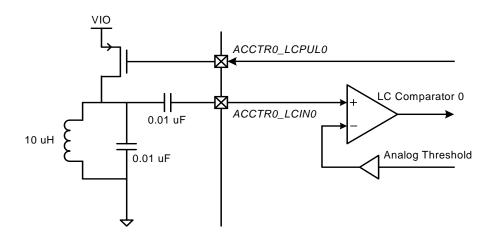

|    | 14.4.Analog Front End                                               |     |    |

|    | 14.5.Analog Comparator Functions                                    |     |    |

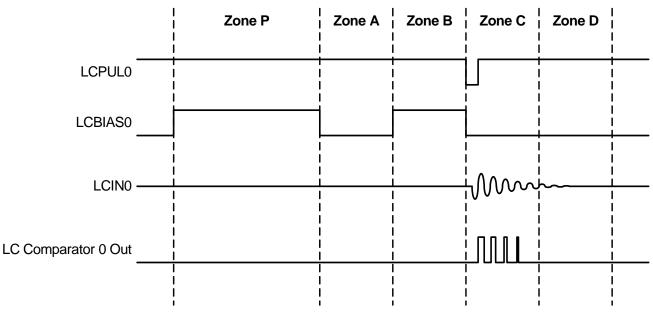

|    | 14.6.LC Counting/Conditioning                                       | . 1 | 61 |

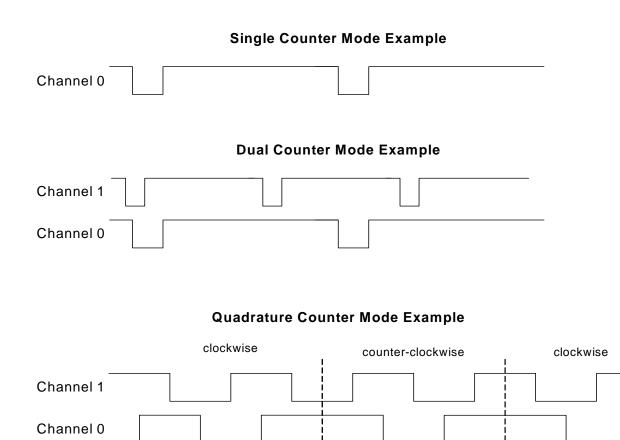

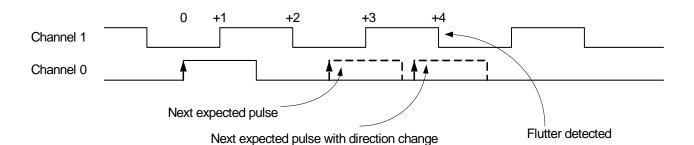

| 14.7.Counting Modes                                       | .164 |

|-----------------------------------------------------------|------|

| 14.8.Sample Rate                                          | .166 |

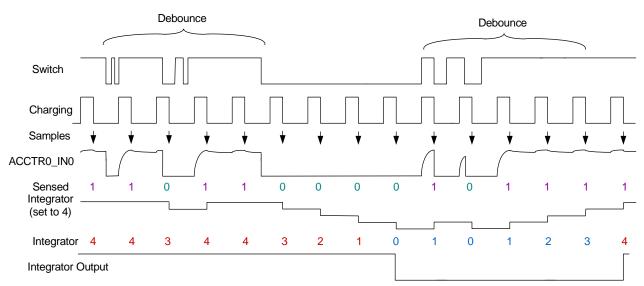

| 14.9.Debounce                                             | .166 |

| 14.10.Reset Behavior                                      |      |

| 14.11.Wake up and Interrupt Sources                       |      |

| 14.12.Register Write Access                               |      |

| 14.13.Debug Signals                                       |      |

| 14.14.LC Resonant Setup Example                           |      |

| 14.15.ACCTR0 Registers                                    |      |

| 14.16.ACCTR0 Register Memory Map                          | 197  |

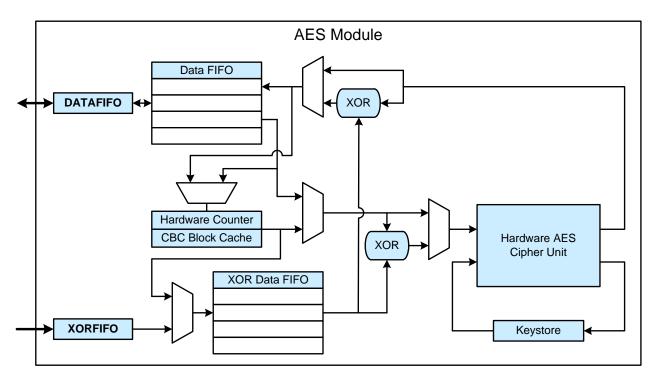

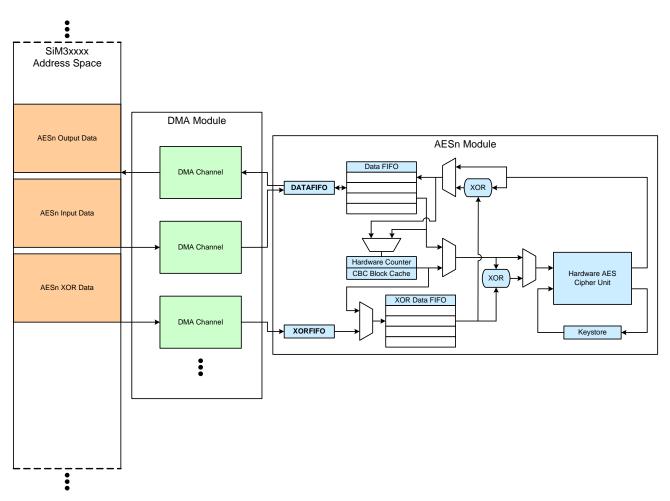

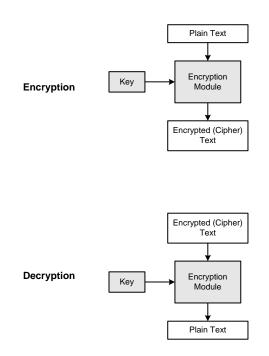

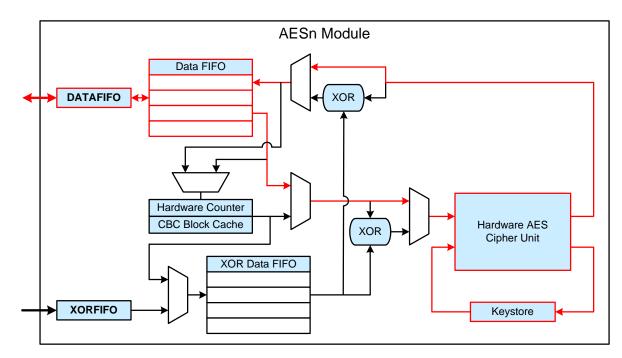

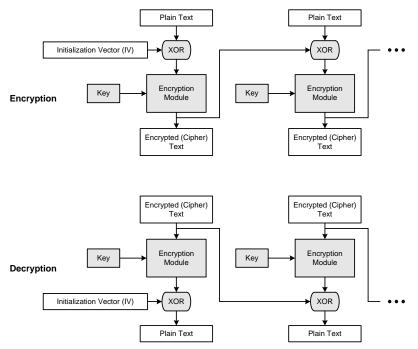

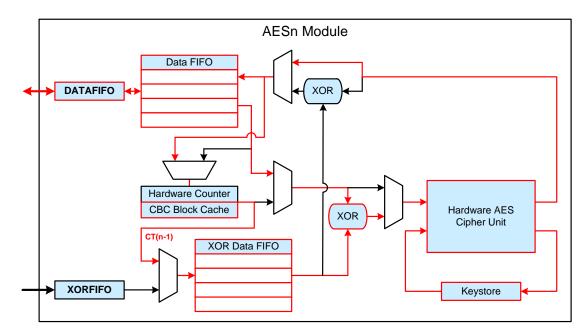

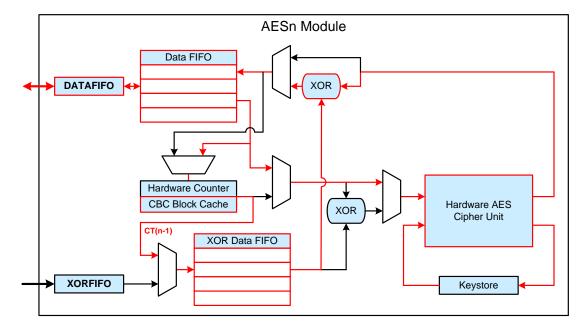

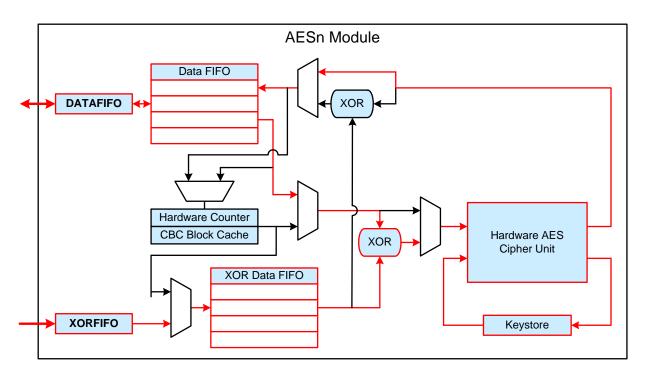

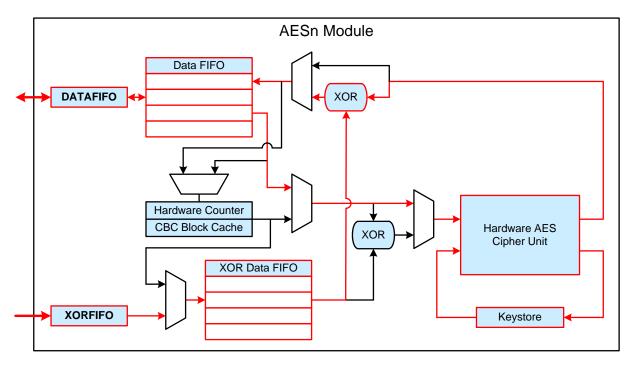

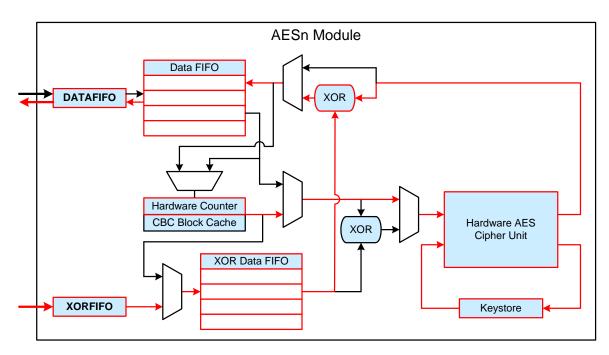

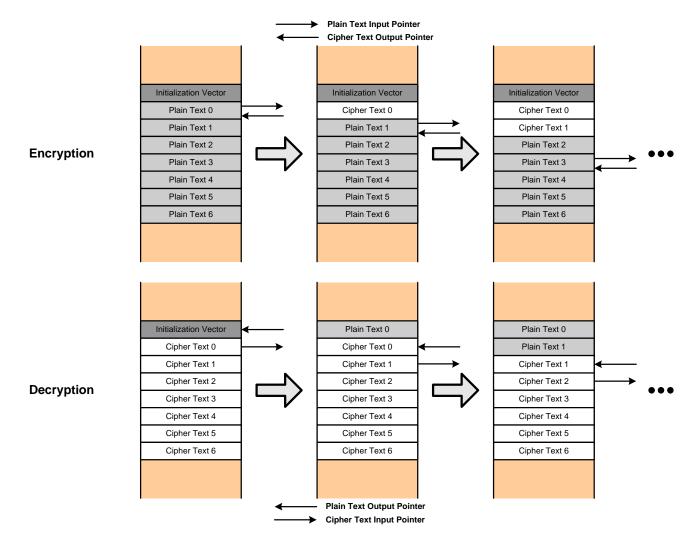

| Advanced Encryption Standard (AES0)                       |      |

| 15.1.AES Features                                         |      |

| 15.2.Overview                                             |      |

| 15.3.Interrupts                                           |      |

| 15.4.Debug Mode                                           |      |

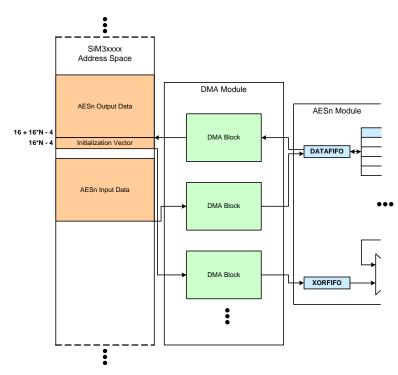

| 15.5.DMA Configuration and Usage                          |      |

| 15.6.Using the AES Module for Electronic Codebook (ECB)   |      |

| 15.7.Using the AES Module for Cipher Block Chaining (CBC) | 208  |

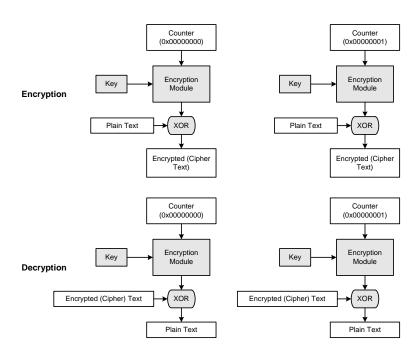

| 15.8.Using the AES Module for Counter (CTR)               |      |

| 15.9.Performing "In-Place" Ciphers                        |      |

| 15.10.Using the AES Module in Software Mode               |      |

| 15.11.AES0 Registers                                      |      |

| 15.12.AES0 Register Memory Map                            |      |

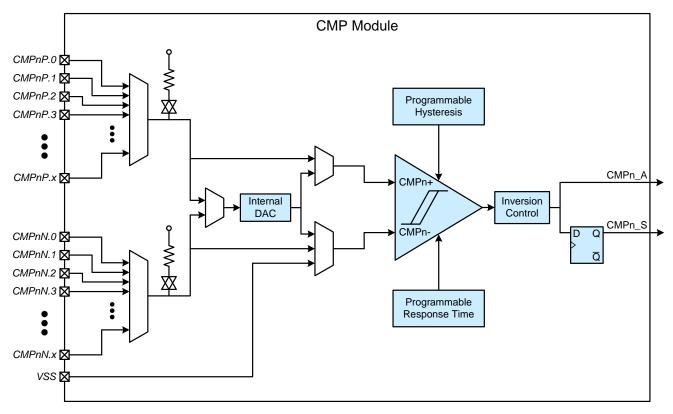

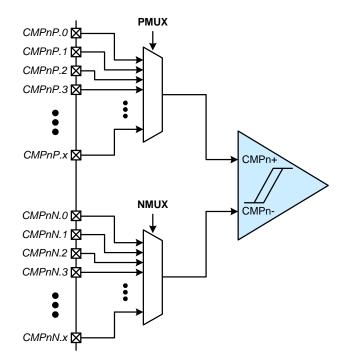

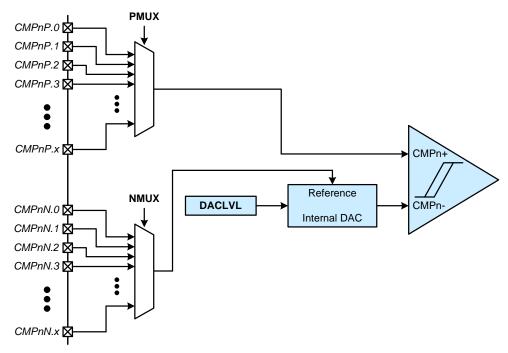

| Comparator (CMP0 and CMP1)                                |      |

| 16.1.Comparator Features                                  |      |

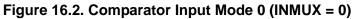

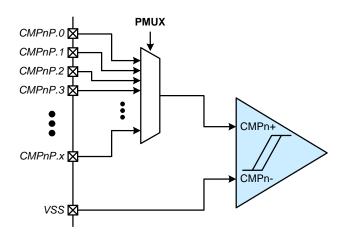

| 16.2.Input Multiplexer                                    |      |

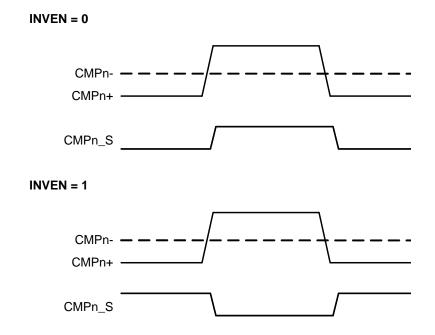

| 16.3.Output Signal Routing                                |      |

| 16.4.Overview                                             |      |

| 16.5.Input Mode Selection                                 |      |

| 16.6.Output Configuration                                 |      |

| 16.7.Response Time                                        |      |

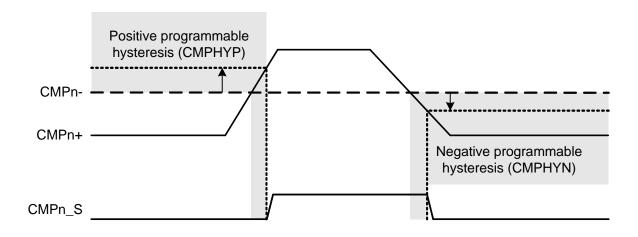

| 16.8.Hysteresis                                           |      |

| 16.9.Interrupts and Flags                                 |      |

| 16.10.CMP0 and CMP1 Registers                             |      |

| 16.11.CMPn Register Memory Map                            |      |

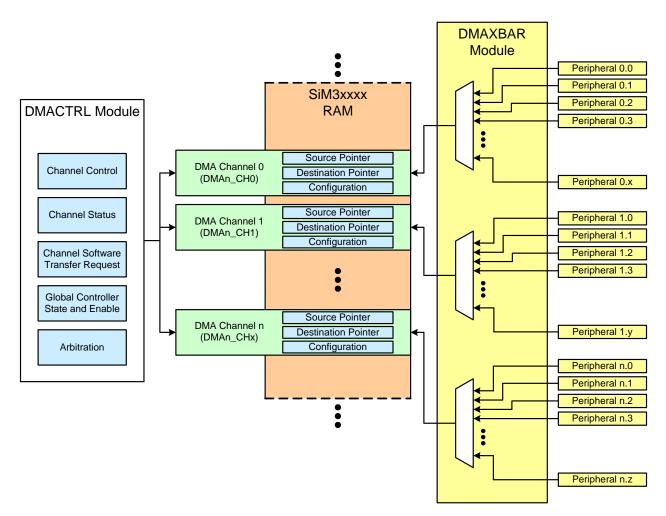

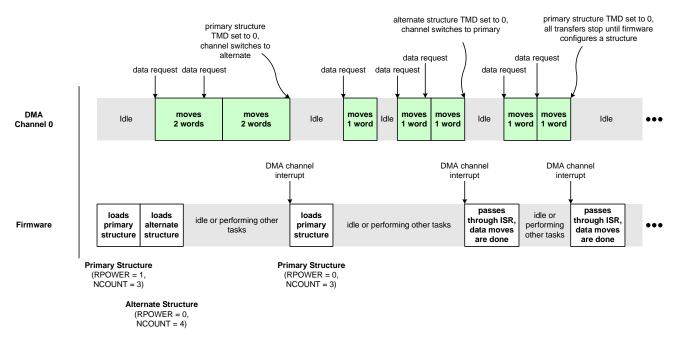

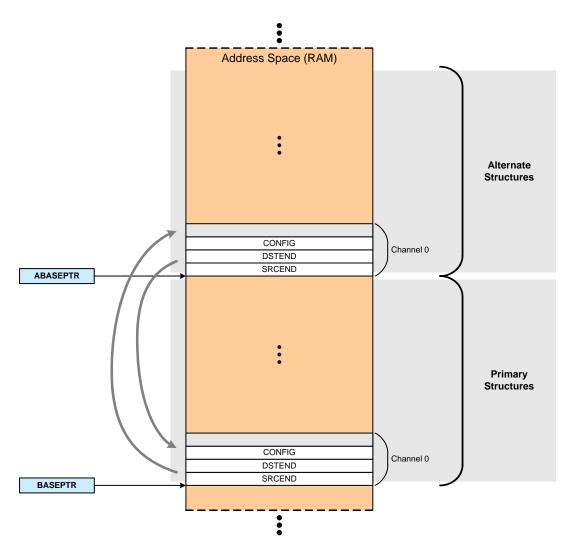

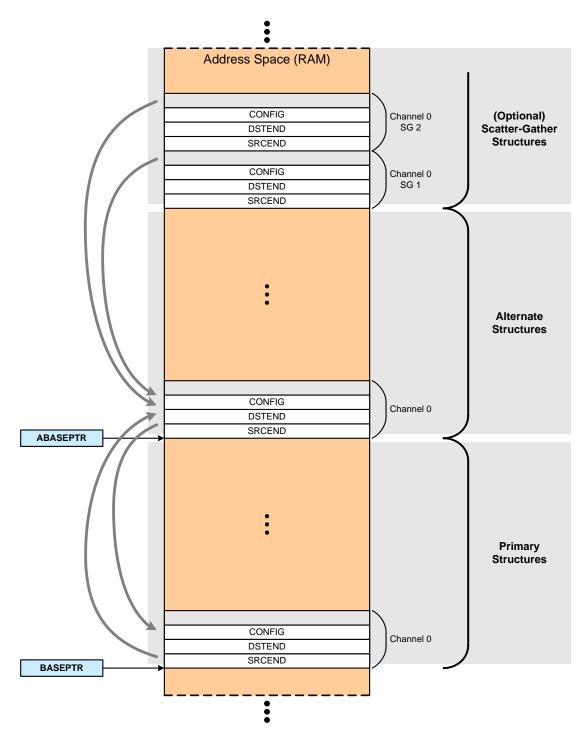

| DMA Controller (DMACTRL0)                                 |      |

| 17.1.DMA Controller Features                              |      |

| 17.2.Overview                                             |      |

| 17.3.Interrupts                                           |      |

| 17.4.Configuring a DMA Channel                            |      |

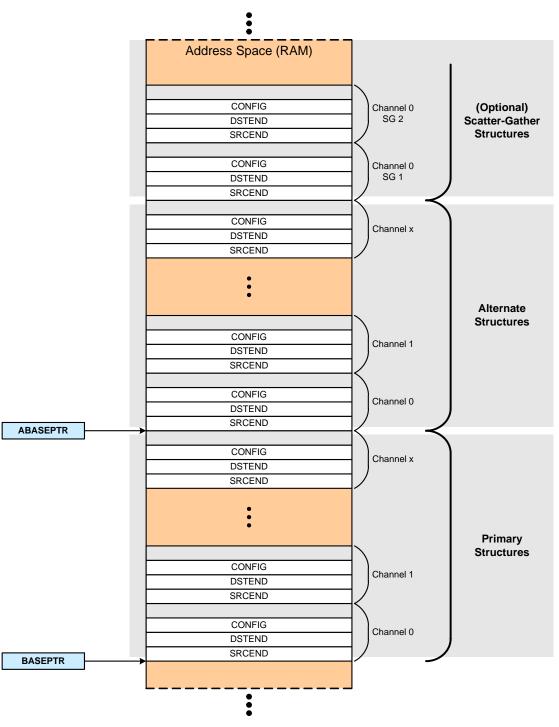

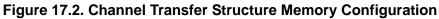

| 17.5.DMA Channel Transfer Structures                      |      |

| 17.6.Transfer Types                                       |      |

| 17.7.Masking Channels                                     |      |

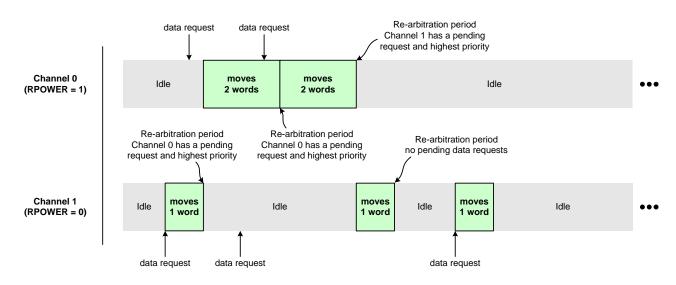

| 17.8.Errors                                               |      |

| 17.9.Arbitration                                          |      |

| 17.10.Data Requests                                       |      |

| •                                                         |      |

| 17.12.DMACTRL0 Register Memory Map         18.DMA Crossbar (DMAXBAR0)         18.1.DMA Crossbar Features         18.2.Channel Priority         18.3.DMAXBAR0 Registers         18.4.DMAXBAR0 Register Memory Map         19.Data Transfer Manager (DTM0, DTM1 and DTM2)         19.1.DTM Features         19.2.Overview         19.3.Counters         19.4.State Machine Control         19.5.Configuring DTM States in Memory         19.6.DTM0, DTM1 and DTM2 Registers         19.7.DTM Register Memory Map         20.Enhanced Cyclic Redundancy Check (ECRC0)         20.1.ECRC Features         20.2.Overview         20.3.Polynomial Specification         20.4.Automatic Seeding         20.5.Peripheral Data Snooping         20.6.DMA Configuration and Usage         20.7.Byte-Level Bit Reversal and Byte Reordering         20.8.ECRC0 Registers         20.9.ECRC0 Registers         20.9.ECRC0 Registers         20.9.ECRC0 Registers         20.9.ECRC0 Registers         21.1.ENCDEC Features         21.2.Manchester Encoding         21.3.Manchester Decoding         21.4.Three-out-of-Six Decoding         21.5.Three-out-of-Six Decoding | 310<br>311<br>312<br>318<br>318<br>319<br>320<br>320<br>321<br>324<br>325<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>331<br>338<br>341<br>349<br>349<br>349<br>349<br>349 |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| <b>18. DMA Crossbar (DMAXBAR0)</b> 18.1. DMA Crossbar Features         18.2. Channel Priority         18.3. DMAXBAR0 Registers         18.4. DMAXBAR0 Register Memory Map <b>19. Data Transfer Manager (DTM0, DTM1 and DTM2)</b> 19.1. DTM Features         19.2. Overview         19.3. Counters         19.4. State Machine Control         19.5. Configuring DTM States in Memory         19.6. DTM0, DTM1 and DTM2 Registers         19.7. DTMn Register Memory Map <b>20. Enhanced Cyclic Redundancy Check (ECRC0)</b> 20.1. ECRC Features         20.2. Overview         20.3. Polynomial Specification         20.4. Automatic Seeding         20.5. Peripheral Data Snooping         20.6. DMA Configuration and Usage         20.7. Byte-Level Bit Reversal and Byte Reordering         20.8. ECRC0 Registers         20.9. ECRC0 Registers         20.9. ECRC0 Register Memory Map         21. Encoder/Decoder (ENCDEC0)         21.1. ENCDEC Features         21.2. Manchester Encoding         21.3. Manchester Encoding         21.4. Three-out-of-Six Encoding                                                                                   | 310<br>311<br>312<br>318<br>318<br>319<br>320<br>320<br>321<br>324<br>325<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>331<br>338<br>341<br>349<br>349<br>349<br>349<br>349 |

| 18.1.DMA Crossbar Features         18.2.Channel Priority         18.3.DMAXBAR0 Registers         18.4.DMAXBAR0 Register Memory Map         19.Data Transfer Manager (DTM0, DTM1 and DTM2)         19.DTM Features         19.2.Overview         19.3.Counters         19.4.State Machine Control         19.5.Configuring DTM States in Memory         19.6.DTM0, DTM1 and DTM2 Registers         19.7.DTM Register Memory Map         20.Enhanced Cyclic Redundancy Check (ECRC0)         20.1.ECRC Features         20.2.Overview         20.3.Polynomial Specification         20.4.Automatic Seeding         20.5.Peripheral Data Snooping         20.6.DMA Configuration and Usage         20.7.Byte-Level Bit Reversal and Byte Reordering         20.8.ECRC0 Registers         20.9.ECRC0 Register Memory Map         21.Encoder/Decoder (ENCDEC0)         21.1.ENCDEC Features         22.9.4.CRC0 Registers         23.9.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2.2                                                                                                                                                                                          | 310<br>311<br>312<br>318<br>319<br>320<br>320<br>321<br>324<br>325<br>325<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>349<br>351               |

| 18.3.DMAXBAR0 Registers         18.4.DMAXBAR0 Register Memory Map.         19.Data Transfer Manager (DTM0, DTM1 and DTM2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 312<br>318<br>319<br>320<br>320<br>321<br>324<br>325<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>338<br>341<br>349<br>349<br>349<br>349                                           |

| 18.4.DMAXBAR0 Register Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 318<br>319<br>320<br>320<br>321<br>324<br>325<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                  |

| 18.4.DMAXBAR0 Register Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 318<br>319<br>320<br>320<br>321<br>324<br>325<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                  |

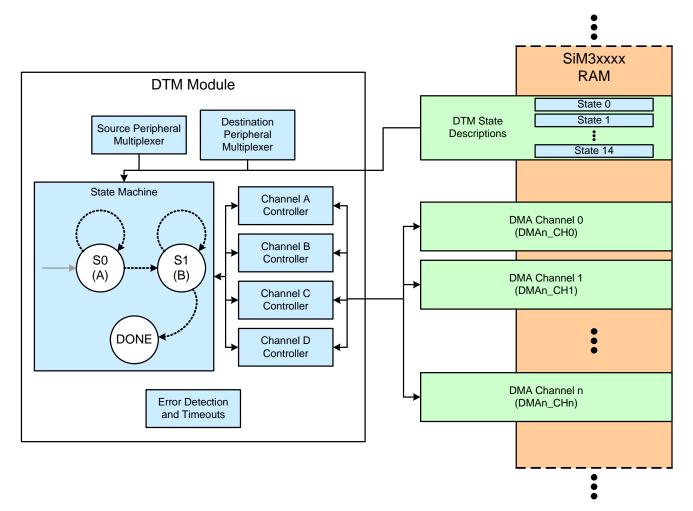

| <ul> <li>19. Data Transfer Manager (DTM0, DTM1 and DTM2)</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 319<br>320<br>320<br>321<br>324<br>325<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>331<br>341<br>349<br>349<br>349<br>349                                                  |

| 19.1.DTM Features         19.2.Overview         19.3.Counters         19.4.State Machine Control         19.5.Configuring DTM States in Memory         19.6.DTM0, DTM1 and DTM2 Registers         19.7.DTMn Register Memory Map.         20.Enhanced Cyclic Redundancy Check (ECRC0)         20.1.ECRC Features         20.2.Overview         20.3.Polynomial Specification         20.4.Automatic Seeding         20.5.Peripheral Data Snooping         20.6.DMA Configuration and Usage         20.7.Byte-Level Bit Reversal and Byte Reordering         20.8.ECRC0 Registers         20.9.ECRC0 Register Memory Map         21.Encoder/Decoder (ENCDEC0)         21.1.ENCDEC Features         21.3.Manchester Encoding         21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                               | 319<br>320<br>321<br>324<br>325<br>332<br>334<br>335<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>338<br>341<br>349<br>349<br>349                                                                       |

| 19.2.Overview         19.3.Counters         19.4.State Machine Control         19.5.Configuring DTM States in Memory         19.6.DTM0, DTM1 and DTM2 Registers         19.7.DTMn Register Memory Map         20. Enhanced Cyclic Redundancy Check (ECRC0)         20.1.ECRC Features.         20.2.Overview         20.3.Polynomial Specification         20.4.Automatic Seeding.         20.5.Peripheral Data Snooping.         20.6.DMA Configuration and Usage         20.7.Byte-Level Bit Reversal and Byte Reordering.         20.8.ECRC0 Registers         20.9.ECRC0 Register Memory Map         21.1.ENCDEC Features.         21.2.Manchester Encoding.         21.3.Manchester Decoding.         21.4.Three-out-of-Six Encoding.                                                                                                                                                                                                                                                                                                                                                                                                                     | 320<br>321<br>324<br>325<br>332<br>332<br>334<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                     |

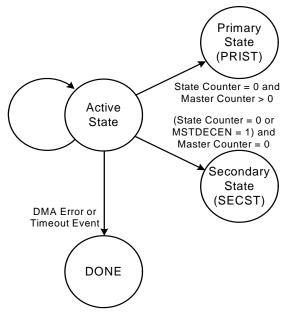

| 19.4.State Machine Control         19.5.Configuring DTM States in Memory.         19.6.DTM0, DTM1 and DTM2 Registers         19.7.DTMn Register Memory Map.         20. Enhanced Cyclic Redundancy Check (ECRC0)         20.1.ECRC Features.         20.2.Overview         20.3.Polynomial Specification         20.4.Automatic Seeding.         20.5.Peripheral Data Snooping.         20.6.DMA Configuration and Usage         20.7.Byte-Level Bit Reversal and Byte Reordering.         20.8.ECRC0 Registers.         20.9.ECRC0 Register Memory Map.         21.Encoder/Decoder (ENCDEC0)         21.1.ENCDEC Features.         21.2.Manchester Encoding         21.3.Manchester Decoding         21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                           | 321<br>324<br>325<br>332<br><b>334</b><br>335<br>335<br>335<br>336<br>337<br>338<br>338<br>341<br>349<br>349<br><b>351</b>                                                                                     |

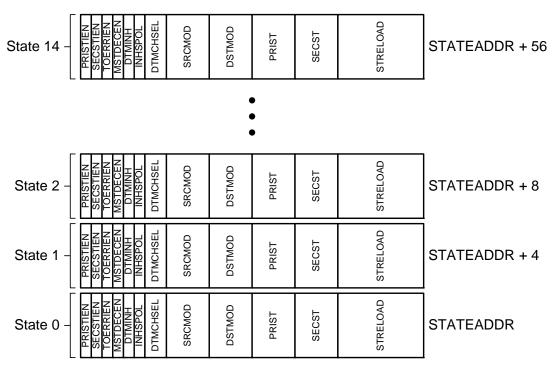

| 19.5.Configuring DTM States in Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 324<br>325<br>332<br>334<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                 |

| 19.5.Configuring DTM States in Memory                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 324<br>325<br>332<br>334<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                 |

| 19.6.DTM0, DTM1 and DTM2 Registers         19.7.DTMn Register Memory Map. <b>20. Enhanced Cyclic Redundancy Check (ECRC0)</b> 20.1.ECRC Features.         20.2.Overview         20.3.Polynomial Specification         20.4.Automatic Seeding.         20.5.Peripheral Data Snooping.         20.6.DMA Configuration and Usage         20.7.Byte-Level Bit Reversal and Byte Reordering.         20.8.ECRC0 Registers.         20.9.ECRC0 Register Memory Map <b>21.Encoder/Decoder (ENCDEC0)</b> 21.1.ENCDEC Features.         21.2.Manchester Encoding         21.3.Manchester Decoding         21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 325<br>332<br>334<br>335<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                 |

| <ul> <li>19.7.DTMn Register Memory Map</li></ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 332<br>334<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                               |

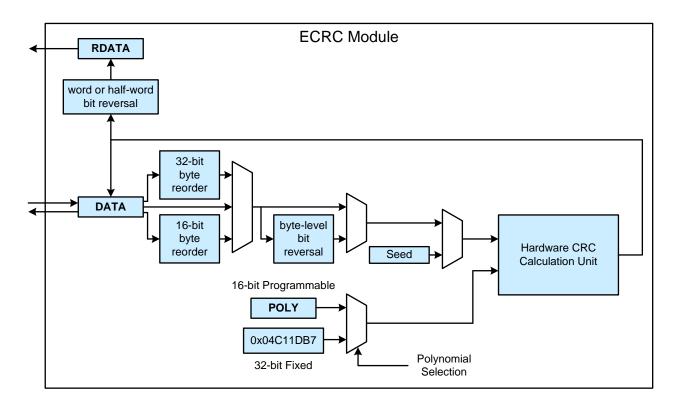

| <ul> <li>20. Enhanced Cyclic Redundancy Check (ECRC0)</li> <li>20.1.ECRC Features</li> <li>20.2.Overview</li> <li>20.3.Polynomial Specification</li> <li>20.4.Automatic Seeding</li> <li>20.5.Peripheral Data Snooping</li> <li>20.6.DMA Configuration and Usage</li> <li>20.7.Byte-Level Bit Reversal and Byte Reordering</li> <li>20.8.ECRC0 Registers</li> <li>20.9.ECRC0 Register Memory Map</li> <li>21. Encoder/Decoder (ENCDEC0)</li> <li>21.1.ENCDEC Features</li> <li>21.2.Manchester Encoding</li> <li>21.3.Manchester Decoding</li> <li>21.4.Three-out-of-Six Encoding</li> </ul>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 334<br>335<br>335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                                      |

| 20.1.ECRC Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 334<br>335<br>335<br>336<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                                      |

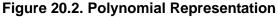

| 20.2.Overview<br>20.3.Polynomial Specification<br>20.4.Automatic Seeding<br>20.5.Peripheral Data Snooping<br>20.6.DMA Configuration and Usage<br>20.7.Byte-Level Bit Reversal and Byte Reordering<br>20.8.ECRC0 Registers<br>20.9.ECRC0 Register Memory Map<br>21.Encoder/Decoder (ENCDEC0)<br>21.1.ENCDEC Features<br>21.2.Manchester Encoding<br>21.3.Manchester Decoding<br>21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 335<br>335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                                                    |

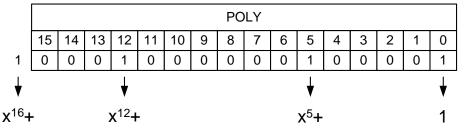

| 20.3.Polynomial Specification                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 335<br>336<br>337<br>338<br>341<br>349<br>349<br>351                                                                                                                                                           |

| 20.4.Automatic Seeding<br>20.5.Peripheral Data Snooping<br>20.6.DMA Configuration and Usage<br>20.7.Byte-Level Bit Reversal and Byte Reordering<br>20.8.ECRC0 Registers<br>20.9.ECRC0 Register Memory Map<br><b>21.Encoder/Decoder (ENCDEC0)</b><br>21.1.ENCDEC Features<br>21.2.Manchester Encoding<br>21.3.Manchester Decoding<br>21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 335<br>336<br>337<br>338<br>341<br>349<br><b>351</b>                                                                                                                                                           |

| 20.5.Peripheral Data Snooping<br>20.6.DMA Configuration and Usage<br>20.7.Byte-Level Bit Reversal and Byte Reordering<br>20.8.ECRC0 Registers<br>20.9.ECRC0 Register Memory Map<br>21.Encoder/Decoder (ENCDEC0)<br>21.1.ENCDEC Features<br>21.2.Manchester Encoding<br>21.3.Manchester Decoding<br>21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 336<br>337<br>338<br>341<br>349<br><b>351</b>                                                                                                                                                                  |

| 20.6.DMA Configuration and Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 337<br>338<br>341<br>349<br><b> 351</b>                                                                                                                                                                        |

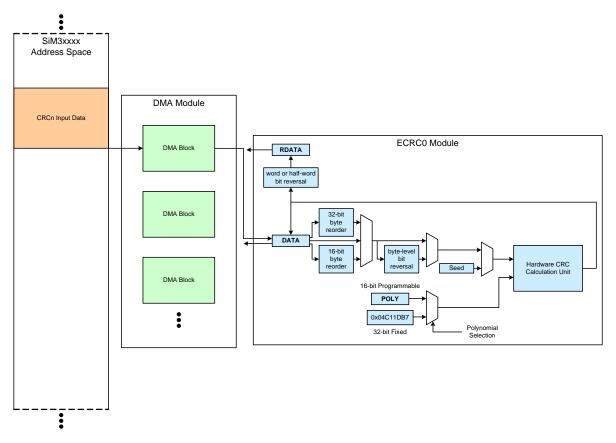

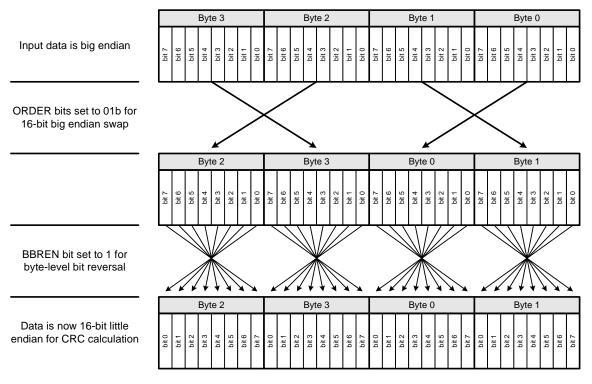

| 20.7.Byte-Level Bit Reversal and Byte Reordering<br>20.8.ECRC0 Registers<br>20.9.ECRC0 Register Memory Map<br><b>21.Encoder/Decoder (ENCDEC0)</b><br>21.1.ENCDEC Features<br>21.2.Manchester Encoding<br>21.3.Manchester Decoding<br>21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 338<br>341<br>349<br><b> 351</b>                                                                                                                                                                               |

| 20.8.ECRC0 Registers<br>20.9.ECRC0 Register Memory Map<br><b>21.Encoder/Decoder (ENCDEC0)</b><br>21.1.ENCDEC Features<br>21.2.Manchester Encoding<br>21.3.Manchester Decoding<br>21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 341<br>349<br><b>351</b>                                                                                                                                                                                       |

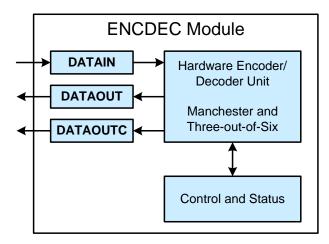

| 21. Encoder/Decoder (ENCDEC0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 351                                                                                                                                                                                                            |

| 21. Encoder/Decoder (ENCDEC0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 351                                                                                                                                                                                                            |

| 21.1.ENCDEC Features<br>21.2.Manchester Encoding<br>21.3.Manchester Decoding<br>21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                |

| 21.3.Manchester Decoding<br>21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |                                                                                                                                                                                                                |

| 21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 352                                                                                                                                                                                                            |

| 21.4.Three-out-of-Six Encoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 353                                                                                                                                                                                                            |

| 21.5.Three-out-of-Six Decoding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 355                                                                                                                                                                                                            |

| 21.6.Interrupts and Error Conditions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 356                                                                                                                                                                                                            |

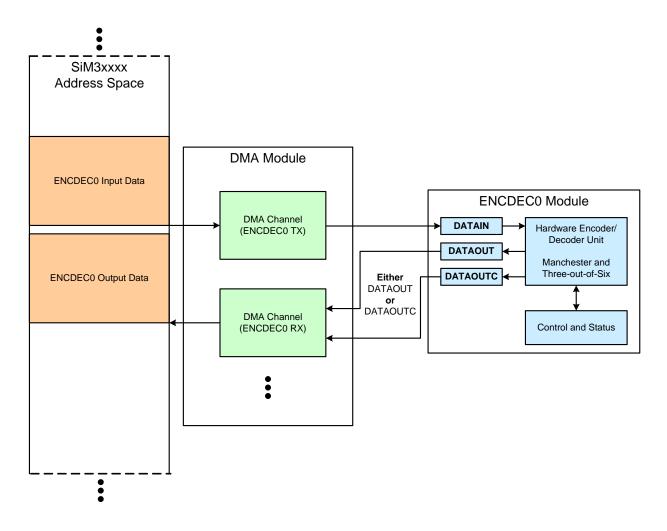

| 21.7.DMA Configuration and Usage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 357                                                                                                                                                                                                            |

| 21.8.ENCDEC0 Registers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                                                                                                |

| 21.9.ENCDEC0 Register Memory Map                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                                                                                                                                                                                |

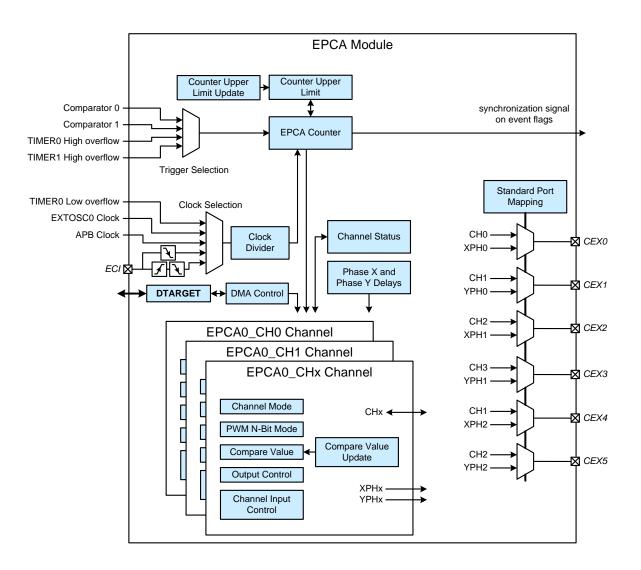

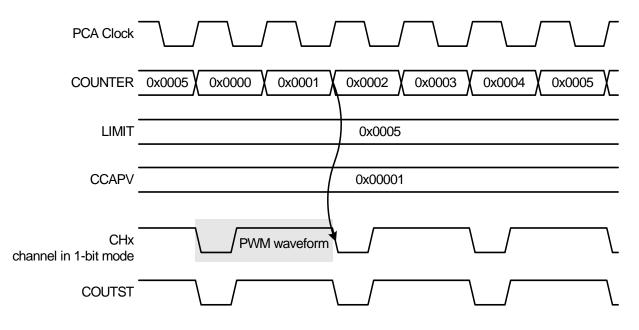

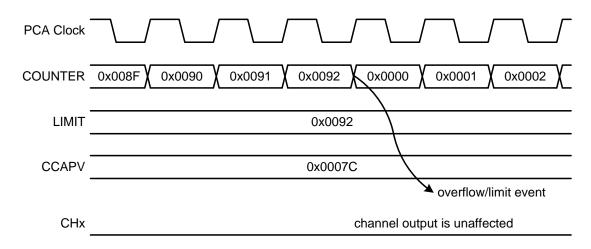

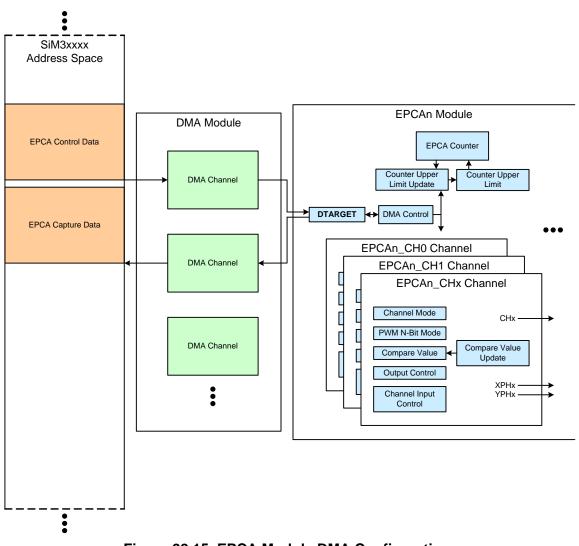

| 22. Enhanced Programmable Counter Array (EPCA0)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 367                                                                                                                                                                                                            |

| 22.1.Enhanced Programmable Counter Array Features                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 367                                                                                                                                                                                                            |

| 22.2.Output Mapping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                                                                                |

| 22.3.Triggers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 369                                                                                                                                                                                                            |

| 22.4.Module Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 369                                                                                                                                                                                                            |

| 22.5.Interrupts                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 369<br>370                                                                                                                                                                                                     |

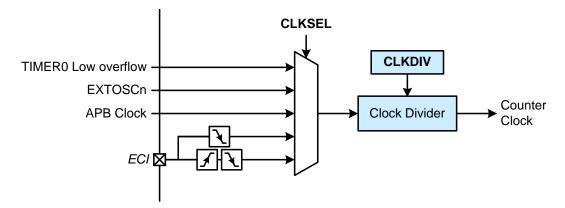

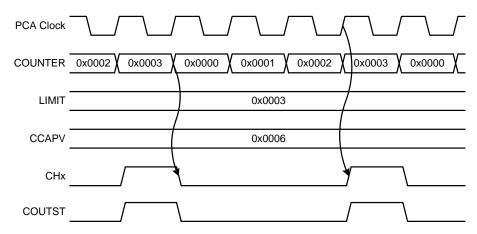

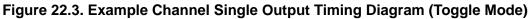

| 22.5.Interrupts<br>22.6.Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 369<br>370<br>370                                                                                                                                                                                              |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 369<br>370<br>370<br>371                                                                                                                                                                                       |

| 22.6.Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 369<br>370<br>370<br>371<br>372                                                                                                                                                                                |

| 22.6.Clocking                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 369<br>370<br>370<br>371<br>372<br>374<br>385                                                                                                                                                                  |

|    | 22.11.EPCA0 Register Memory Map                  | .400 |

|----|--------------------------------------------------|------|

|    | 22.12.EPCA0_CH0-5 Registers                      |      |

|    | 22.13.EPCAn_CHx Register Memory Map              |      |

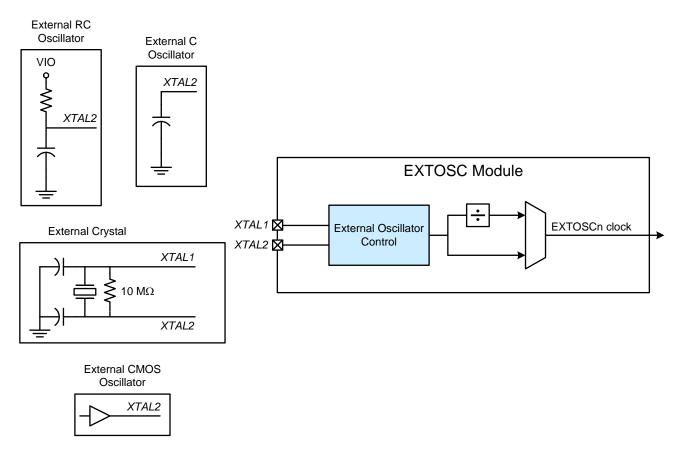

| 23 | External Oscillator (EXTOSC0)                    |      |

|    | 23.1.External Oscillator Features                |      |

|    | 23.2.External Pin Connections                    | .411 |

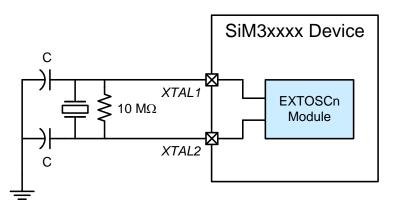

|    | 23.3.External Crystal Oscillator                 | .411 |

|    | 23.4.External CMOS Oscillator                    |      |

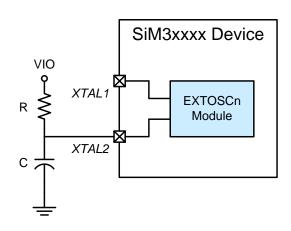

|    | 23.5.External RC Oscillator                      | .413 |

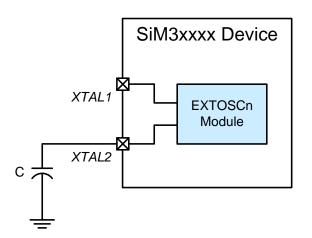

|    | 23.6.External C Oscillator                       | .415 |

|    | 23.7.EXTOSC0 Registers                           | .417 |

|    | 23.8.EXTOSC0 Register Memory Map                 | .419 |

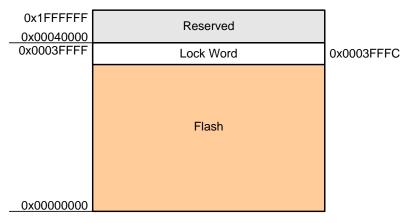

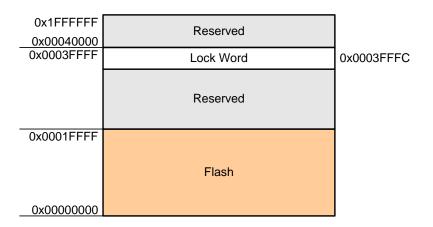

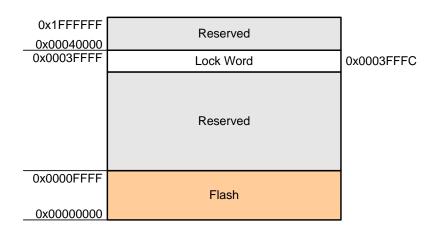

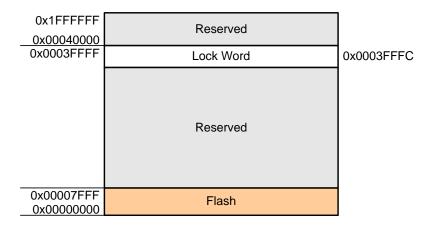

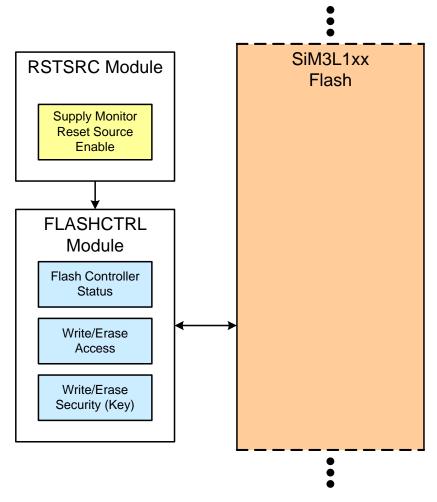

| 24 | Flash Controller (FLASHCTRL0)                    | 420  |

|    | 24.1.Flash Controller Features                   |      |

|    | 24.2.Overview                                    | .421 |

|    | 24.3.Flash Read Control                          | .421 |

|    | 24.4.Flash Write and Erase Control               | .422 |

|    | 24.5.FLASHCTRL0 Registers                        | .425 |

|    | 24.6.FLASHCTRL0 Register Memory Map              | .431 |

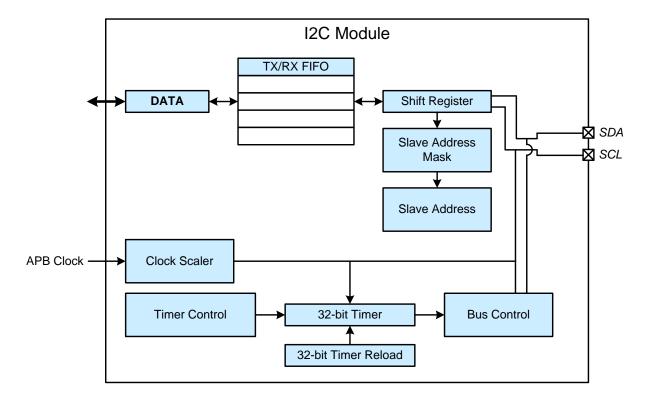

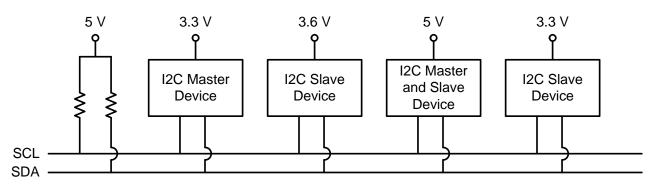

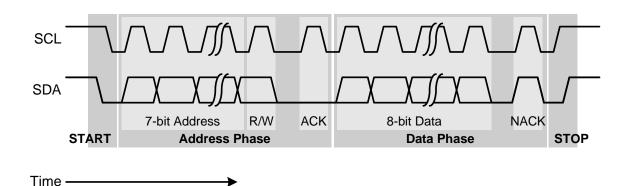

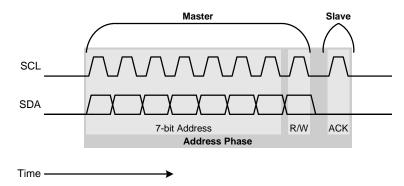

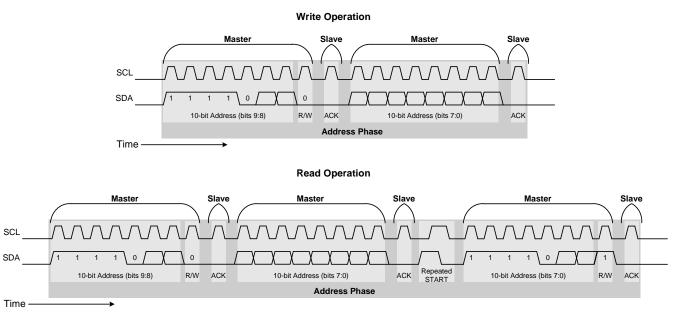

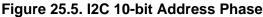

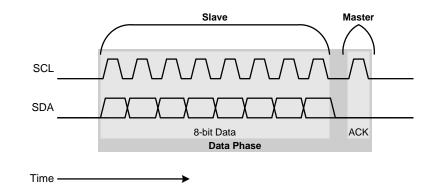

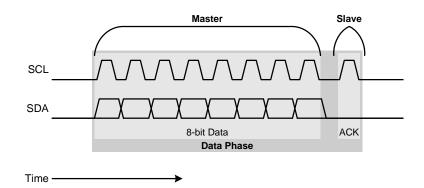

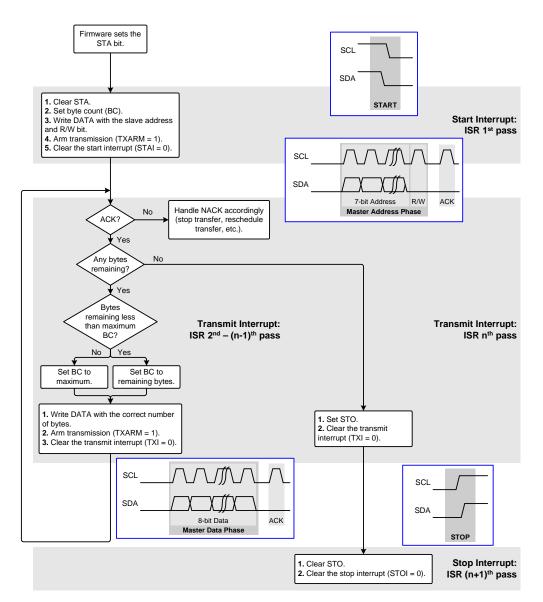

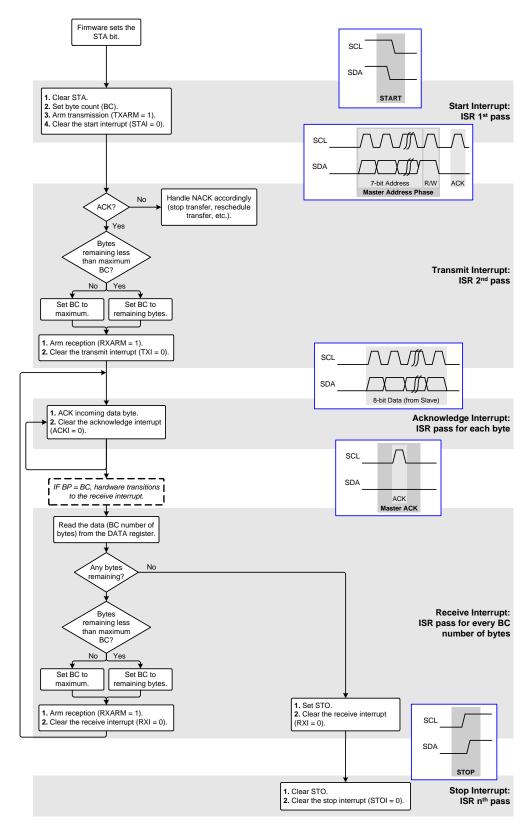

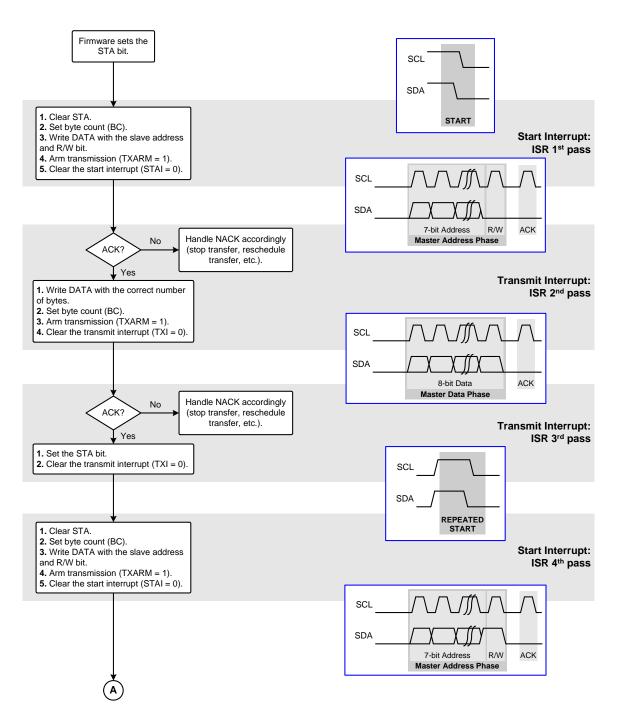

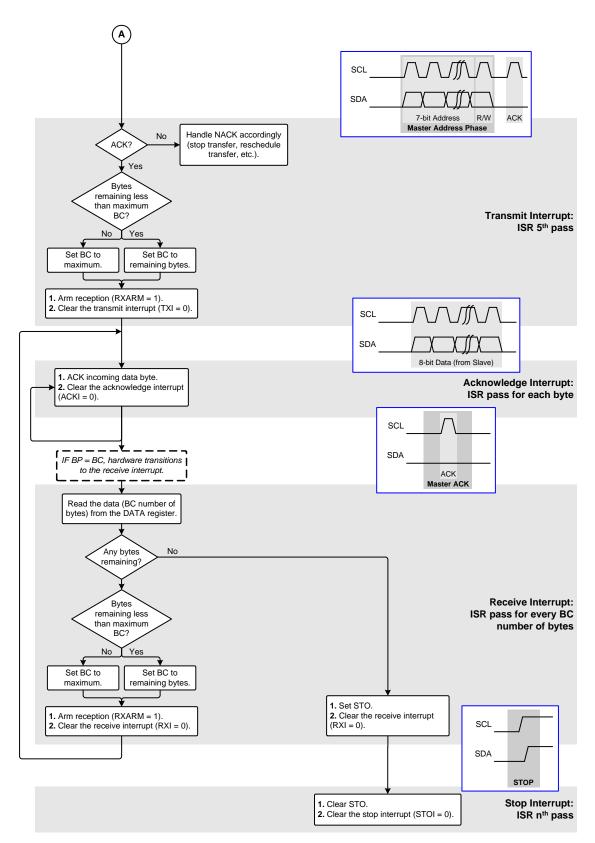

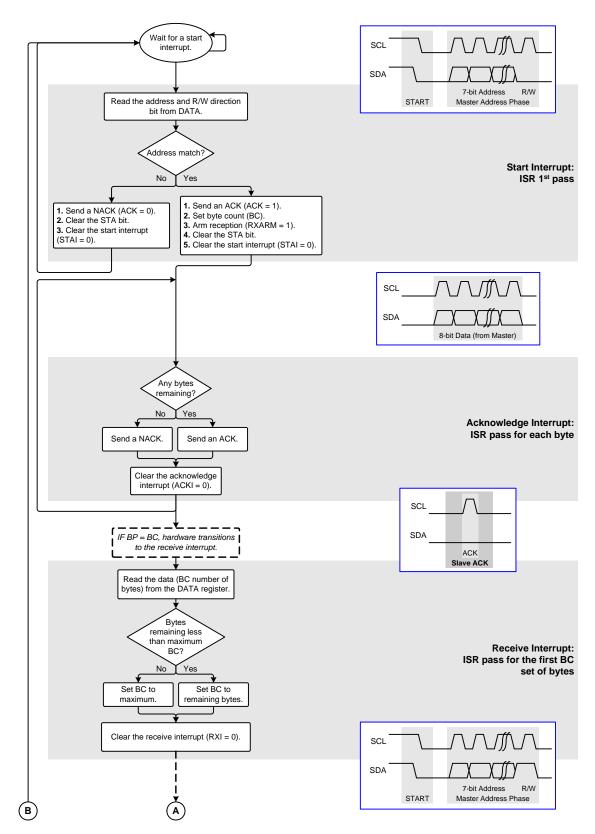

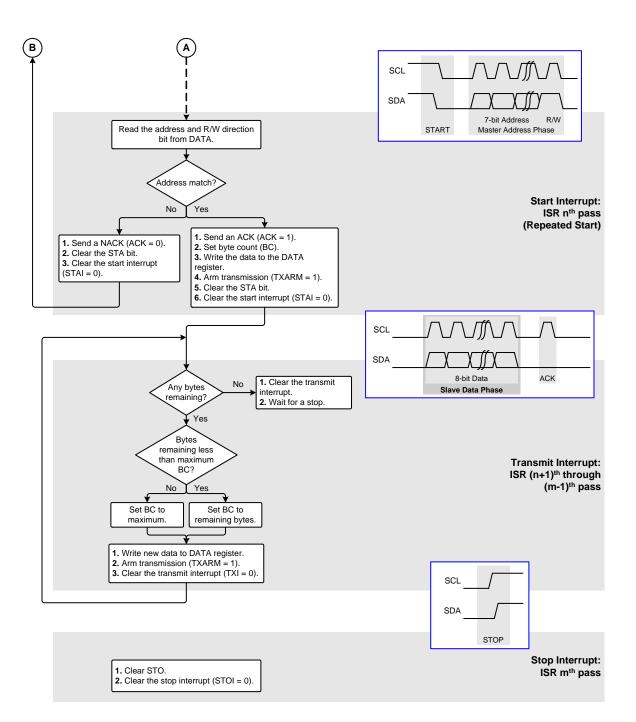

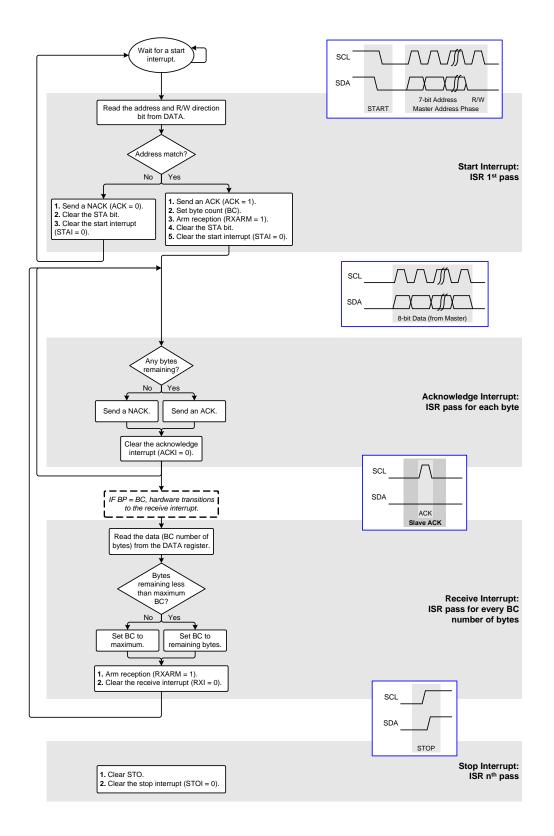

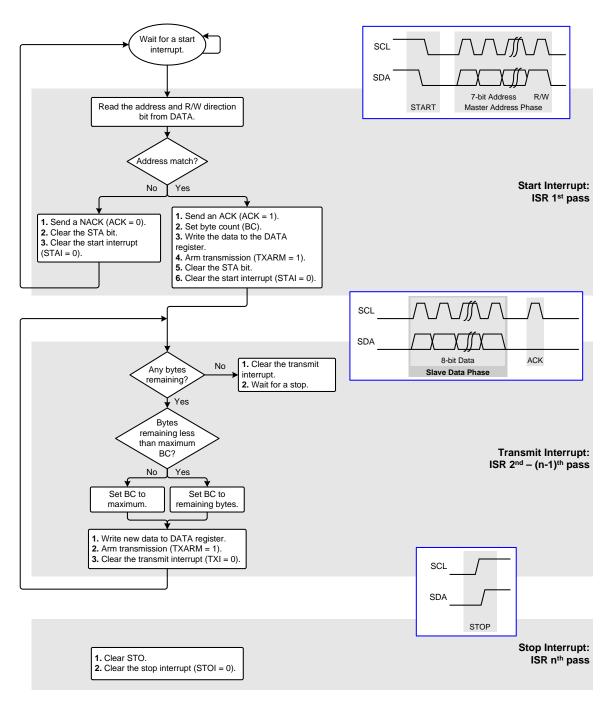

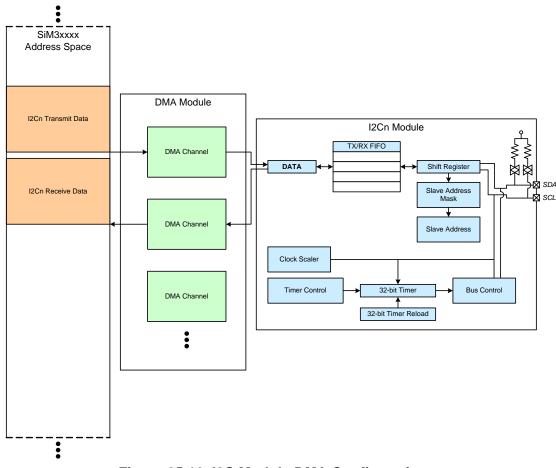

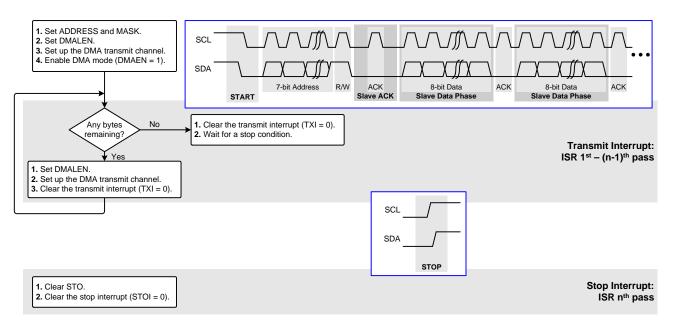

| 25 | Inter-Integrated Circuit Bus (I2C0)              |      |

|    | 25.1.I2C Features                                | .433 |

|    | 25.2.Signal Routing                              | .433 |

|    | 25.3.I2C Protocol                                | .434 |

|    | 25.4.Clocking                                    | .438 |

|    | 25.5.Operational Modes                           | .438 |

|    | 25.6.Error Handling                              |      |

|    | 25.7.Additional Features                         | .452 |

|    | 25.8.Debug Mode                                  | .453 |

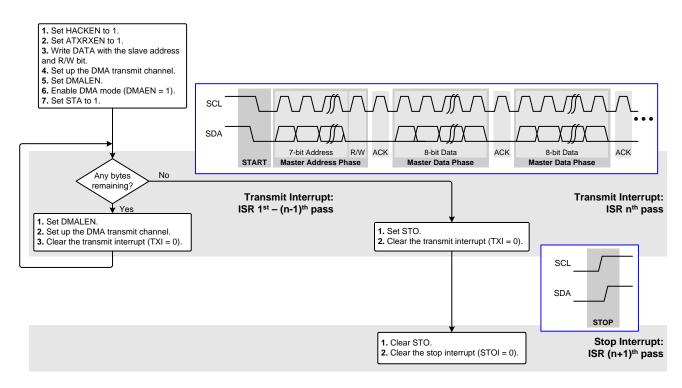

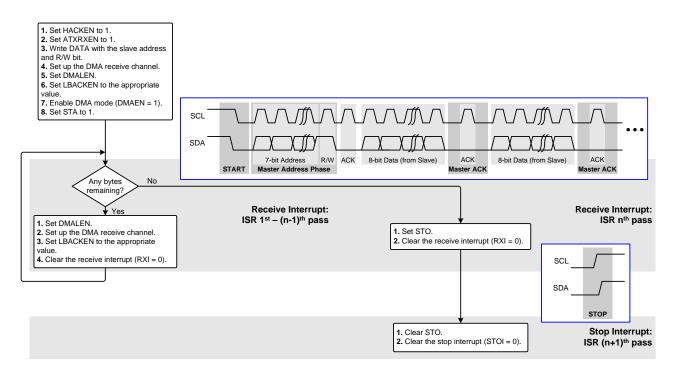

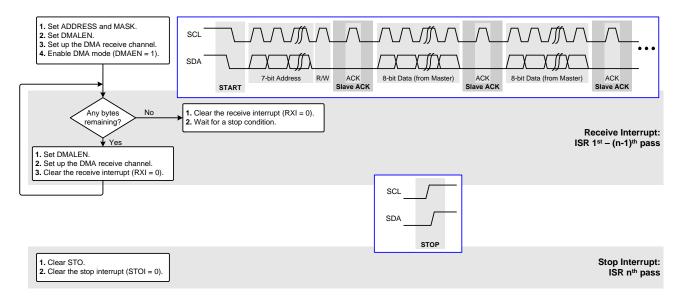

|    | 25.9.DMA Configuration and Usage                 | .454 |

|    | 25.10.I2C0 Registers                             | .459 |

|    | 25.11.I2C0 Register Memory Map                   |      |

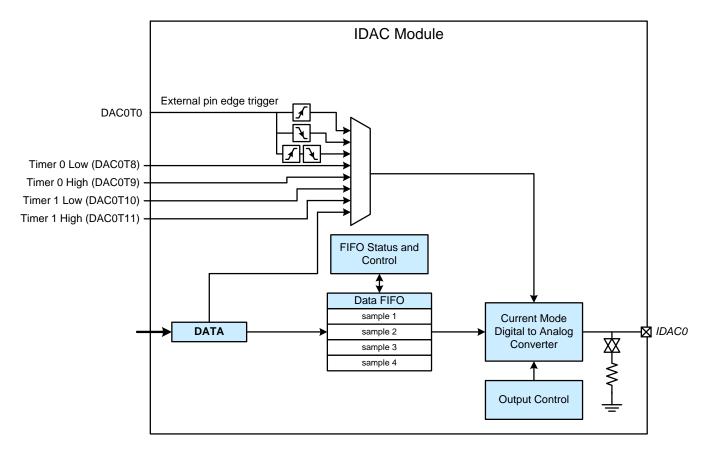

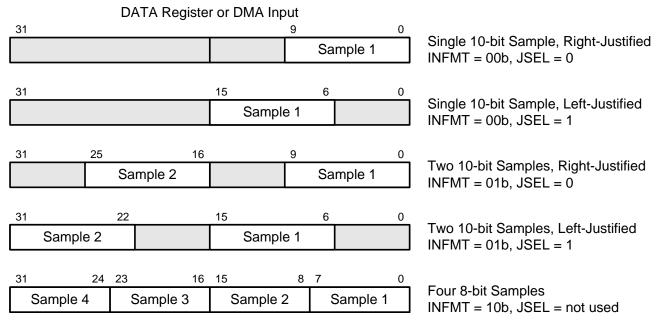

| 26 | Current Mode Digital-to-Analog Converter (IDAC0) | .477 |

|    | 26.1.IDAC Features                               | .477 |

|    | 26.2.Output                                      | .478 |

|    | 26.3.Conversion Triggers                         | .478 |

|    | 26.4.IDAC Setup                                  | .479 |

|    | 26.5.Using the IDAC in On-Demand Mode            |      |

|    | 26.6.Using the IDAC in Periodic FIFO-Only Mode   |      |

|    | 26.7.Using the IDAC in Periodic FIFO Wrap Mode   |      |

|    | 26.8.Using the IDAC in Periodic DMA Mode         |      |

|    | 26.9.Adjusting the IDAC Output Current           |      |

|    | 26.10.Debug Mode                                 |      |

|    | 26.11.IDAC0 Registers                            |      |

|    | 26.12.IDAC0 Register Memory Map                  |      |

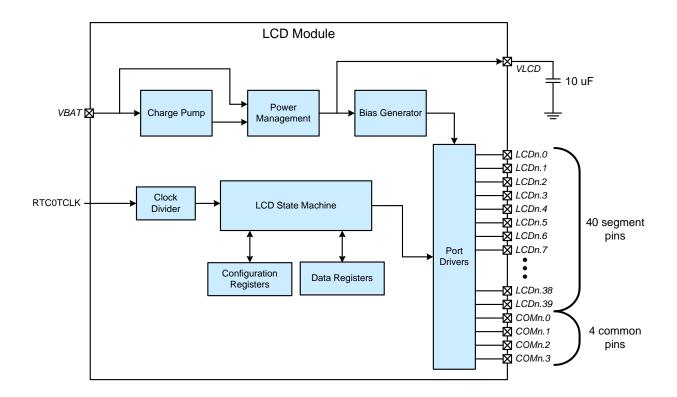

| 27 | LCD Controller (LCD0)                            |      |

|    | 27.1.LCD Features                                | .493 |

|     | 27.2.Pin Assignment                                 | 494 |

|-----|-----------------------------------------------------|-----|

|     | 27.3.Configuring the Segment Driver                 |     |

|     | 27.4.Powering Down                                  |     |

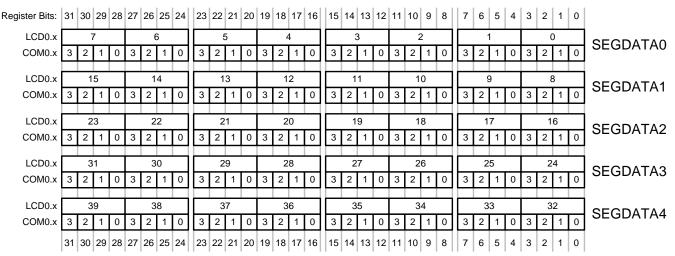

|     | 27.5.Mapping Data Registers to LCD Pins             |     |

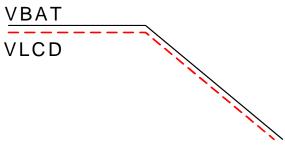

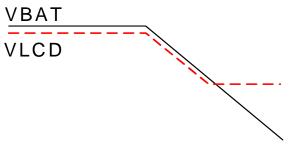

|     | 27.6.Contrast Adjustment                            |     |

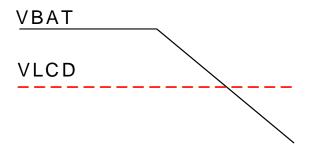

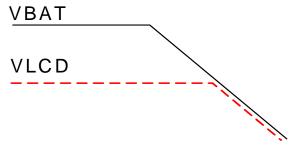

|     | 27.7.Adjusting the VBAT Monitor Threshold           |     |

|     | 27.8.Setting the Refresh Rate                       |     |

|     | 27.9.Blinking Segments                              |     |

|     | 27.10.LCD0 Registers                                |     |